Descoberta avança três gerações na construção de chips

Redação do Site Inovação Tecnológica - 22/01/2007

Imagine utilizar transistores do mesmo tamanho daqueles que equipam os chips atuais, mas conseguir criar circuitos até oito vezes mais densos. E, de quebra, consumindo menos energia - vale dizer, esquentando menos - do que os microprocessadores atuais para um mesmo cálculo computacional.

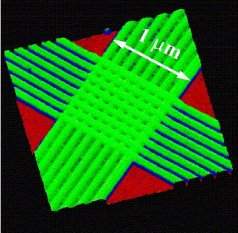

Esta é a promessa de uma nova tecnologia anunciada por dois cientistas que trabalham para a empresa HP. Gregory Snider e Stan Williams utilizaram simulações computacionais para chegar a uma nova arquitetura baseada em uma chave transversal ("crossbar") nanoscópica, um nanofio montado acima do tradicional CMOS ("Complementary Metal Oxide Silicon").

Os novos chips podem ser fabricados com os mesmos transistores utilizados na construção dos atuais chips FPGA ("Field Programmable Gate Array"). Chips FPGA são circuitos integrados com interconexões e componentes de lógica programável que podem ser adaptados para aplicações específicas pelo usuário final.

"O que nós conseguimos fazer foi combinar a tecnologia CMOS convencional com dispositivos de chaveamento em nanoescala em um circuito híbrido, para aumentar a densidade efetiva dos transistores, reduzir a dissipação de energia e aumentar dramaticamente a tolerância a defeitos," disse Stan Williams.

A nova arquitetura foi batizada de FPNI ("Field Programmable Nanowire Interconnect"), já que é um melhoramento da FPGA. Todas as operações lógicas são feitas no CMOS, enquanto a maioria do roteamento dos sinais é feito pela estrutura "crossbar" que fica acima da camada dos transistores. Como a arquitetura FPGA utiliza entre 80 e 90% de seu CMOS para roteamento de sinais, a nova arquitetura FPNI é muito mais eficiente. A densidade dos transistores efetivamente utilizados para a parte lógica do chip é muito maior e a quantidade de eletricidade exigida para o roteamento dos sinais é muito menor.

Para se ter uma idéia do avanço, a nova arquitetura salta nada menos do que as três próximas gerações previstas na tecnologia de construção de chips, e sem ter que diminuir o tamanho dos transistores.

Artigo: Nano/CMOS architectures using a field-programmable nanowire interconnect

Autores: Gregory S. Snider, R. Stanley Williams

Revista: Nanotechnology

Data: Jan. 24 2007

Vol.: Volume 18, Number 3

DOI: 10.1088/0957-4484/18/3/035204

Link: http://www.iop.org/EJ/article/0957-4484/18/3/035204/nano7_3_035204.pdf

Energia das ondas é extraída com eficiência ótima usando giroscópios

Como projetar juntas robóticas tão eficientes quanto nossos joelhos

Tempo quântico pode ser medido sem um relógio

Um feixe de luz vira dois com características completamente diferentes

Descoberto material metálico com condutividade térmica recorde

Processador fotônico roda por horas a temperatura ambiente

Buracos de minhoca não existem, Big Bang é um portal e o tempo vai e vem, propõem físicos

Armazenar dados em DNA é mais fácil do que se pensava

Bateria de ferrugem melhora com o tempo, guardando cada vez mais carga

Cristal do tempo levita e desafia Terceira Lei de Newton

Descoberto material metálico com condutividade térmica recorde

Um micromotor preciso o suficiente para microcirurgias

Escultura eletrônica: Componentes têm propriedades ditadas pela geometria

Será que agora a eletrônica de diamante decola?

Laser de som cria terremoto dentro de um chip

Memória quântica é feita com luz presa em gaiolas de luz

Todos os direitos reservados.

É proibida a reprodução total ou parcial, por qualquer meio, sem prévia autorização por escrito.