Chip de 6 andares detona recordes de miniaturização e velocidade

Redação do Site Inovação Tecnológica - 20/10/2025

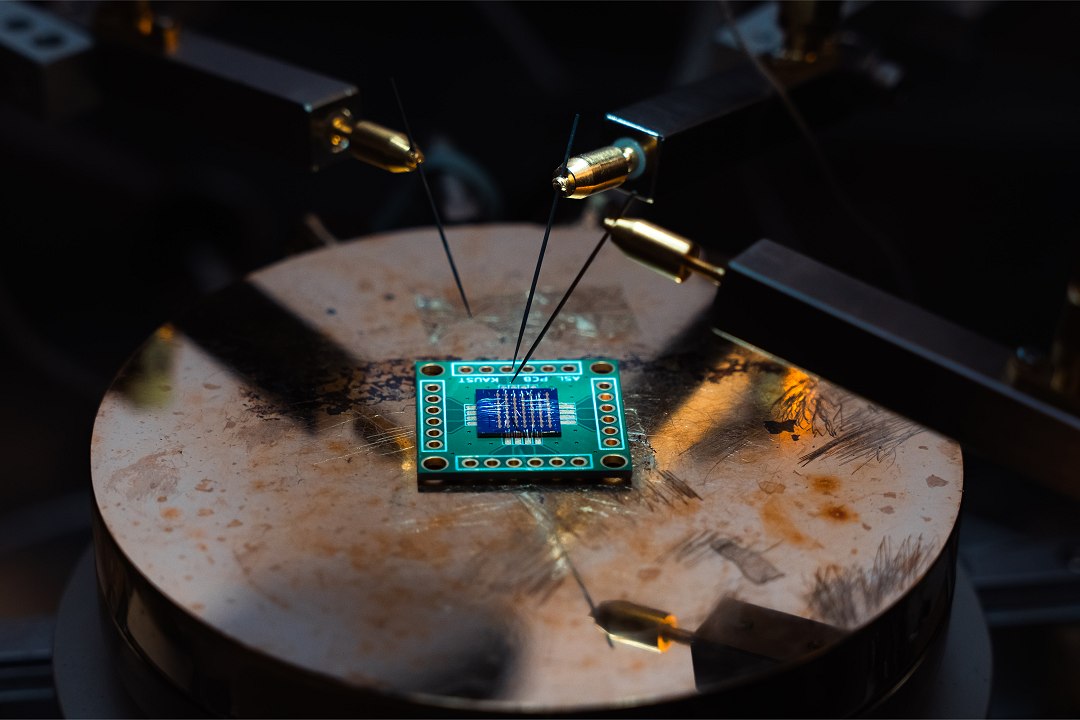

[Imagem: KAUST]

Chip 3D de seis andares

Com a crescente aproximação dos limites dos componentes eletrônicos, uma das principais estratégias para aumentar a velocidade dos computadores está na fabricação de chips 3D, criando estruturas empilhadas que diminuem o tempo necessário para que os dados desloquem-se de um componente para outro.

Os chips em formato de sobrado - com dois andares - já são comuns, mas Saravanan Yuvaraja e colegas da Universidade de Ciência e Tecnologia Rei Abdullah, na Arábia Saudita, acabam de detonar todos os recordes desses edifícios eletrônicos.

A equipe projetou e construiu o primeiro chip CMOS híbrido de seis camadas para eletrônica de grande porte. Como nenhum outro circuito integrado híbrido tinha excedido até agora as duas pilhas, este feito marca um novo padrão em termos de densidade de componentes e eficiência de integração, abrindo possibilidades em miniaturização e desempenho da eletrônica.

Entre as tecnologias da microeletrônica, os circuitos integrados CMOS (semicondutor complementar de óxido metálico) são encontrados em quase todos os eletrônicos, de celulares e televisores a satélites e dispositivos médicos. E, comparados aos chips de silício convencionais, os microchips CMOS híbridos, como o usado nesta demonstração, são ainda mais promissores para a eletrônica de grandes áreas, colocando mais poder de processamento dentro de cada chip, provendo miniaturização adicional e ganhos de velocidade.

[Imagem: Saravanan Yuvaraja et al. - 10.1038/s41928-025-01469-0]

Potência em menos espaço

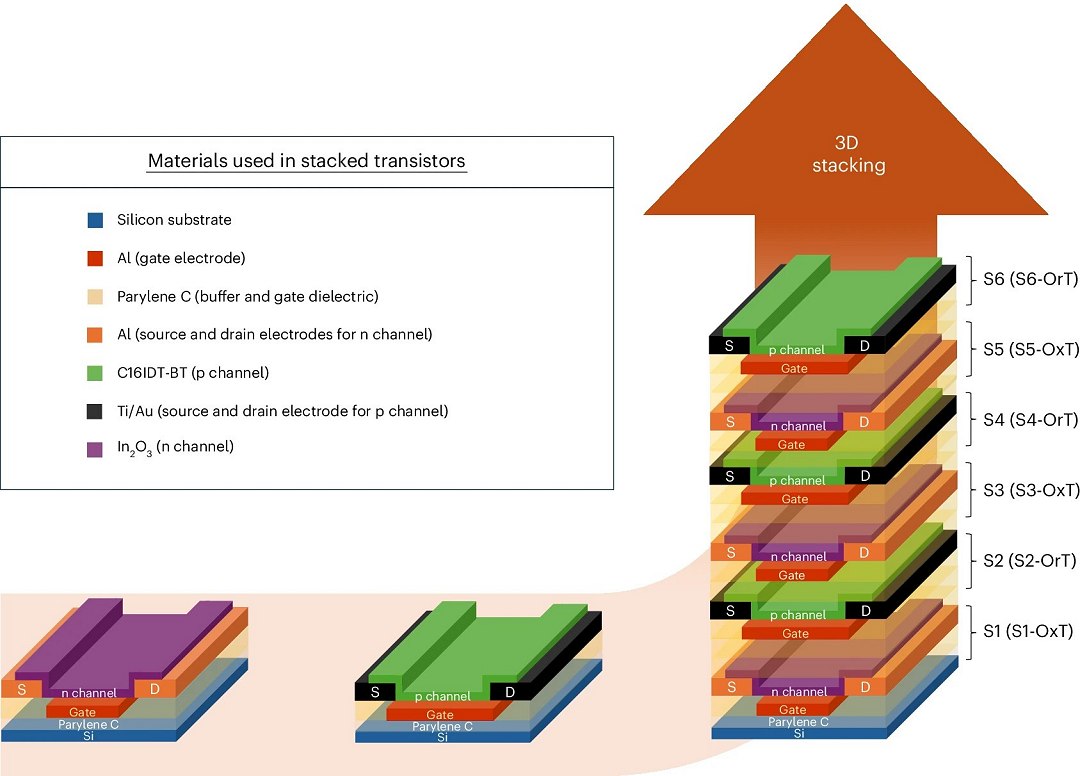

A fabricação de circuitos integrados tipicamente requer temperaturas de centenas de graus Celsius, o que acaba danificando os andares inferiores do chip 3D à medida que novos andares são adicionados. No novo processo, nenhuma etapa de fabricação excedeu 150 °C - impedindo danos às camadas anteriormente depositadas - na verdade, a maioria das etapas foi concluída quase à temperatura ambiente.

Outra exigência é que a superfície das camadas deve ser o mais lisa possível, para que os componentes possam ser depositados de modo perfeitamente alinhado - para o empilhamento vertical funcionar, as camadas devem ser alinhadas corretamente, para uma conexão ideal entre os componentes. Também aqui a nova técnica superou a concorrência, permitindo chegar aos seis andares.

"No projeto de microchips, tudo envolve reunir mais potência em menos espaço. Ao refinar várias etapas da fabricação, fornecemos um modelo para escalar verticalmente e aumentar a densidade funcional muito além dos limites atuais," disse Yuvaraja.

Artigo: Three-Dimensional Integrated Hybrid Complementary Circuits for Large-Area Electronics

Autores: Saravanan Yuvaraja, Mohamad Insan Nugraha, Qiao He, Leo Raj Solay, Patsy Arely Miranda Cortez, Na Xiao, Martin Heeney, Thomas D. Anthopoulos, Xiaohang Li

Revista: Nature Electronics

DOI: 10.1038/s41928-025-01469-0

Rede de lasers viabiliza exploração da Lua com energia solar

Estado exótico da matéria é criado com luz dentro de um chip

Luz manipula a matéria de maneiras inesperadas

Serragem de madeira é transformada em material resistente ao fogo

Medimos a força da gravidade de novo. E o resultado não bateu

Baterias de semente de girassol poderão alimentar nosso futuro

Material tem rigidez alterada remotamente por ondas sonoras

Calor amolece metais, mas muito calor torna metais muito mais fortes

Gerador inédito produz eletricidade consumindo gases de efeito estufa

Astrônomos encontram fronteira final da formação de estrelas na Via Láctea

Chips cerebrais vão se dissolver depois de fazerem seu trabalho

Estado exótico da matéria é criado com luz dentro de um chip

Implante neural menor que um grão de sal consegue ler seu cérebro

Componente fotônico lê 80 mil HDs de uma vez

Geometria oculta curva elétrons como a gravidade curva a luz

Tecnologias quânticas avançam, mas continuam longe das fábricas

Todos os direitos reservados.

É proibida a reprodução total ou parcial, por qualquer meio, sem prévia autorização por escrito.