Pesquisador comenta caminhos rumo à computação 3D

Com informações da Agência Fapesp - 04/10/2013

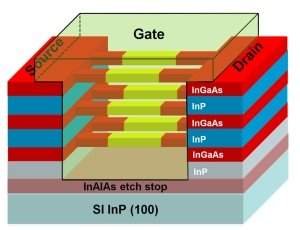

[Imagem: Jiangjiang Gu et al.]

Na busca por aparelhos eletrônicos cada vez mais poderosos, um componente tem destaque especial: o processador.

"Cérebro" de computadores, celulares, tablets, câmeras e outros dispositivos digitais, o chip tem o desafio de ser sempre mais rápido mesmo tendo que lidar com uma quantidade de informações que não para de crescer.

Se fosse humano, teria que ser uma mistura de Usain Bolt e Albert Einstein.

Os processadores atuais lidam com informações em um tipo de memória, chamada de acesso aleatório (RAM), no qual os dados digitais fluem em duas dimensões. Mas e se fossem tridimensionais? As informações passariam não apenas pelos planos X e Y de um gráfico, mas também pelo Z. Como se fosse sair do chão de uma cabana para um edifício de muitos andares.

É justamente essa proposta que tem motivado os estudos no grupo dirigido pelo físico Russell Cowburn, da Universidade de Cambridge, no Reino Unido, um dos expoentes na área.

Cowburn foi um dos palestrantes no evento FAPESP Week London, simpósio realizado na Royal Society, em Londres.

Chips tridimensionais

Segundo Cowburn, ao evoluir para plataformas tridimensionais, os chips poderão levar a um aumento de diversas vezes na performance dos dispositivos eletrônicos.

Melhores, mas não maiores. Ao passar de uma camada para várias, os chips não ganhariam em tamanho, outra preocupação da indústria eletrônica.

"Um típico microchip tem cerca de 1 milímetro de espessura, mas as coisas interessantes ocorrem em uma finíssima camada com cerca de 1 micrômetro [milionésima parte do metro] no topo. Isso significa que 1 milésimo do volume atual de um chip é usado para as funções 'inteligentes'. O resto é embalagem e substrato", disse Cowburn.

"Mesmo levando em consideração os chips atuais, temos o potencial de colocar dezenas, centenas ou milhares de camadas sem ter de mudar o tamanho do dispositivo", disse o cientista.

Em teoria, já parece complicado, mas na prática é ainda mais. Para transformar os resultados das pesquisas feitas em Cambridge em tecnologias de mercado, serão necessárias mudanças também no funcionamento básico dos eletrônicos.

"Precisamos aprender, por exemplo, como dissipar o calor do interior do chip tridimensional. Temos também que descobrir como fazer com o fluxo de informação, com sua velocidade. Meu ponto de vista é que serão necessários novos níveis básicos, novos princípios físicos para poder aproveitar as vantagens da arquitetura tridimensional. Não podemos construir os circuitos eletrônicos atuais em 3D", disse Cowburn.

Spintrônica

Enquanto outros laboratórios têm pesquisado sucessores do silício para os chips do futuro, o grupo de Cowburn tem preferido utilizar uma alternativa híbrida.

"Usamos silício na base, onde fica a parte microeletrônica convencional. E dali para cima temos as partes que lidam com os processos, no nosso caso, utilizando a spintrônica", disse.

A spintrônica é uma tecnologia emergente - já presente em dispositivos comerciais - que explora o spin (orientação) dos elétrons e o momento magnético associado, além da carga elétrica (base da eletrônica tradicional).

"Somos um laboratório de física. No momento, estamos explorando novos métodos que permitam que a informação passe de átomo para átomo em uma dimensão que atualmente

Processador fotônico roda por horas a temperatura ambiente

Escultura eletrônica: Componentes têm propriedades ditadas pela geometria

Projetado primeiro detector de grávitons, as partículas da gravidade

Luz é focalizada e desfocada no espaço livre, sem lentes

Descoberto material metálico com condutividade térmica recorde

Computador neuromórfico conecta matemática, inteligência e neurociência

Buracos de minhoca não existem, Big Bang é um portal e o tempo vai e vem, propõem físicos

Cristal do tempo levita e desafia Terceira Lei de Newton

Tensão de Hubble surge da física real, e não de erros de medição

Bateria de nióbio inédita é criada na USP

Descoberto material metálico com condutividade térmica recorde

Um micromotor preciso o suficiente para microcirurgias

Escultura eletrônica: Componentes têm propriedades ditadas pela geometria

Será que agora a eletrônica de diamante decola?

Laser de som cria terremoto dentro de um chip

Memória quântica é feita com luz presa em gaiolas de luz

Todos os direitos reservados.

É proibida a reprodução total ou parcial, por qualquer meio, sem prévia autorização por escrito.